OXC (ਆਪਟੀਕਲ ਕਰਾਸ-ਕਨੈਕਟ) ROADM (ਰੀਕਨਫਿਗਰੇਬਲ ਆਪਟੀਕਲ ਐਡ-ਡ੍ਰੌਪ ਮਲਟੀਪਲੈਕਸਰ) ਦਾ ਇੱਕ ਵਿਕਸਤ ਸੰਸਕਰਣ ਹੈ।

ਆਪਟੀਕਲ ਨੈੱਟਵਰਕਾਂ ਦੇ ਮੁੱਖ ਸਵਿਚਿੰਗ ਤੱਤ ਦੇ ਰੂਪ ਵਿੱਚ, ਆਪਟੀਕਲ ਕਰਾਸ-ਕਨੈਕਟਸ (OXCs) ਦੀ ਸਕੇਲੇਬਿਲਟੀ ਅਤੇ ਲਾਗਤ-ਪ੍ਰਭਾਵਸ਼ੀਲਤਾ ਨਾ ਸਿਰਫ਼ ਨੈੱਟਵਰਕ ਟੌਪੋਲੋਜੀ ਦੀ ਲਚਕਤਾ ਨੂੰ ਨਿਰਧਾਰਤ ਕਰਦੀ ਹੈ ਬਲਕਿ ਵੱਡੇ ਪੈਮਾਨੇ ਦੇ ਆਪਟੀਕਲ ਨੈੱਟਵਰਕਾਂ ਦੇ ਨਿਰਮਾਣ ਅਤੇ ਸੰਚਾਲਨ ਅਤੇ ਰੱਖ-ਰਖਾਅ ਦੀਆਂ ਲਾਗਤਾਂ ਨੂੰ ਵੀ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਪ੍ਰਭਾਵਤ ਕਰਦੀ ਹੈ। ਵੱਖ-ਵੱਖ ਕਿਸਮਾਂ ਦੇ OXC ਆਰਕੀਟੈਕਚਰਲ ਡਿਜ਼ਾਈਨ ਅਤੇ ਕਾਰਜਸ਼ੀਲ ਲਾਗੂਕਰਨ ਵਿੱਚ ਮਹੱਤਵਪੂਰਨ ਅੰਤਰ ਪ੍ਰਦਰਸ਼ਿਤ ਕਰਦੇ ਹਨ।

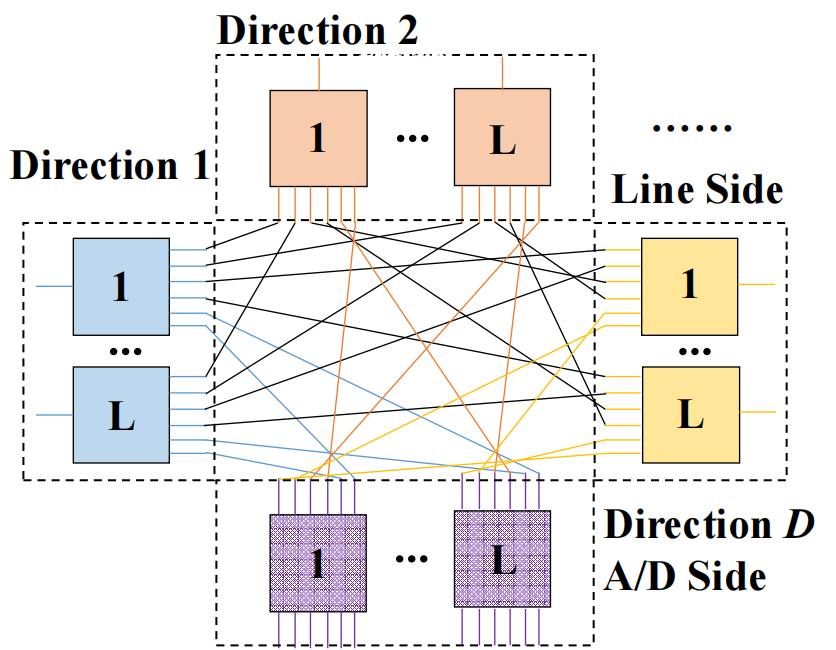

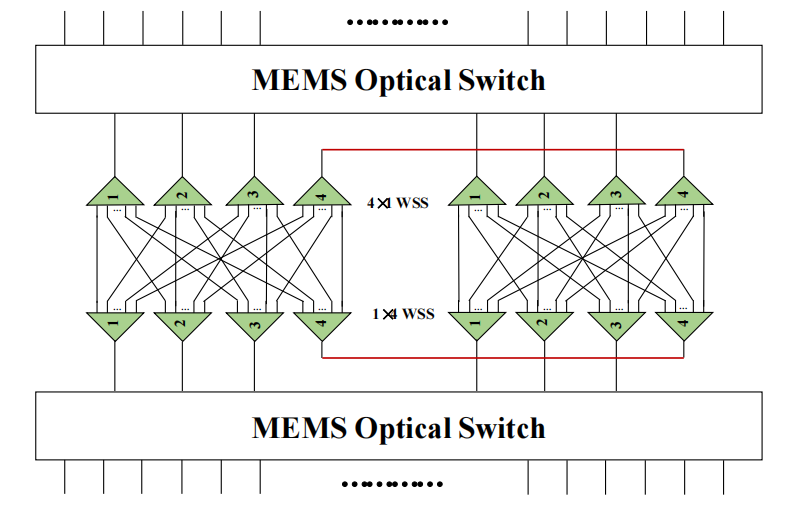

ਹੇਠਾਂ ਦਿੱਤਾ ਚਿੱਤਰ ਇੱਕ ਰਵਾਇਤੀ CDC-OXC (ਰੰਗਹੀਣ ਦਿਸ਼ਾਹੀਣ ਕੰਟੈਂਸ਼ਨਲੈੱਸ ਆਪਟੀਕਲ ਕਰਾਸ-ਕਨੈਕਟ) ਆਰਕੀਟੈਕਚਰ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ, ਜੋ ਕਿ ਵੇਵਲੇਂਥ ਸਿਲੈਕਟਿਵ ਸਵਿੱਚਾਂ (WSSs) ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ। ਲਾਈਨ ਸਾਈਡ 'ਤੇ, 1 × N ਅਤੇ N × 1 WSSs ਇਨਗਰੈਸ/ਐਗਰੈਸ ਮੋਡੀਊਲ ਵਜੋਂ ਕੰਮ ਕਰਦੇ ਹਨ, ਜਦੋਂ ਕਿ ਐਡ/ਡ੍ਰੌਪ ਸਾਈਡ 'ਤੇ M × K WSSs ਵੇਵਲੇਂਥ ਦੇ ਜੋੜ ਅਤੇ ਗਿਰਾਵਟ ਦਾ ਪ੍ਰਬੰਧਨ ਕਰਦੇ ਹਨ। ਇਹ ਮੋਡੀਊਲ OXC ਬੈਕਪਲੇਨ ਦੇ ਅੰਦਰ ਆਪਟੀਕਲ ਫਾਈਬਰਾਂ ਰਾਹੀਂ ਆਪਸ ਵਿੱਚ ਜੁੜੇ ਹੋਏ ਹਨ।

ਚਿੱਤਰ: ਰਵਾਇਤੀ ਸੀਡੀਸੀ-ਓਐਕਸਸੀ ਆਰਕੀਟੈਕਚਰ

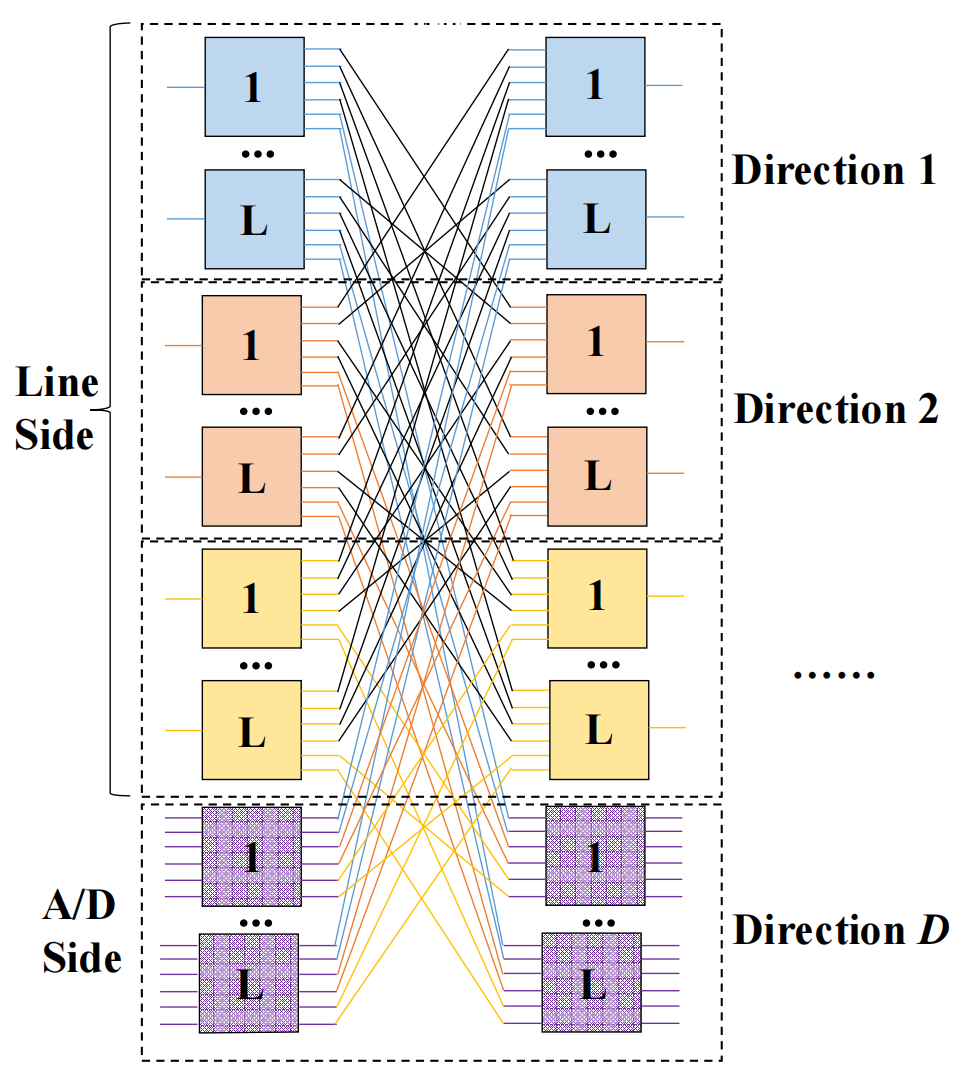

ਇਹ ਬੈਕਪਲੇਨ ਨੂੰ ਸਪੈਂਕ ਨੈੱਟਵਰਕ ਵਿੱਚ ਬਦਲ ਕੇ ਵੀ ਪ੍ਰਾਪਤ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਜਿਸਦੇ ਨਤੀਜੇ ਵਜੋਂ ਸਾਡਾ ਸਪੈਂਕ-ਓਐਕਸਸੀ ਆਰਕੀਟੈਕਚਰ ਬਣਦਾ ਹੈ।

ਚਿੱਤਰ: ਸਪੈਂਕ-ਓਐਕਸਸੀ ਆਰਕੀਟੈਕਚਰ

ਉਪਰੋਕਤ ਚਿੱਤਰ ਦਰਸਾਉਂਦਾ ਹੈ ਕਿ ਲਾਈਨ ਵਾਲੇ ਪਾਸੇ, OXC ਦੋ ਕਿਸਮਾਂ ਦੇ ਪੋਰਟਾਂ ਨਾਲ ਜੁੜਿਆ ਹੋਇਆ ਹੈ: ਦਿਸ਼ਾਤਮਕ ਪੋਰਟ ਅਤੇ ਫਾਈਬਰ ਪੋਰਟ। ਹਰੇਕ ਦਿਸ਼ਾਤਮਕ ਪੋਰਟ ਨੈੱਟਵਰਕ ਟੌਪੋਲੋਜੀ ਵਿੱਚ OXC ਦੀ ਭੂਗੋਲਿਕ ਦਿਸ਼ਾ ਨਾਲ ਮੇਲ ਖਾਂਦਾ ਹੈ, ਜਦੋਂ ਕਿ ਹਰੇਕ ਫਾਈਬਰ ਪੋਰਟ ਦਿਸ਼ਾਤਮਕ ਪੋਰਟ ਦੇ ਅੰਦਰ ਦੋ-ਦਿਸ਼ਾਵੀ ਫਾਈਬਰਾਂ ਦੇ ਇੱਕ ਜੋੜੇ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ। ਇੱਕ ਦਿਸ਼ਾਤਮਕ ਪੋਰਟ ਵਿੱਚ ਕਈ ਦੋ-ਦਿਸ਼ਾਵੀ ਫਾਈਬਰ ਜੋੜੇ (ਭਾਵ, ਮਲਟੀਪਲ ਫਾਈਬਰ ਪੋਰਟ) ਹੁੰਦੇ ਹਨ।

ਜਦੋਂ ਕਿ ਸਪੈਂਕ-ਅਧਾਰਿਤ OXC ਇੱਕ ਪੂਰੀ ਤਰ੍ਹਾਂ ਆਪਸ ਵਿੱਚ ਜੁੜੇ ਬੈਕਪਲੇਨ ਡਿਜ਼ਾਈਨ ਰਾਹੀਂ ਸਖਤੀ ਨਾਲ ਗੈਰ-ਬਲਾਕਿੰਗ ਸਵਿਚਿੰਗ ਪ੍ਰਾਪਤ ਕਰਦਾ ਹੈ, ਇਸਦੀਆਂ ਸੀਮਾਵਾਂ ਨੈੱਟਵਰਕ ਟ੍ਰੈਫਿਕ ਵਧਣ ਦੇ ਨਾਲ-ਨਾਲ ਮਹੱਤਵਪੂਰਨ ਹੋ ਜਾਂਦੀਆਂ ਹਨ। ਵਪਾਰਕ ਵੇਵ-ਲੰਬਾਈ ਚੋਣਵੇਂ ਸਵਿੱਚਾਂ (WSSs) ਦੀ ਪੋਰਟ ਗਿਣਤੀ ਸੀਮਾ (ਉਦਾਹਰਣ ਵਜੋਂ, ਮੌਜੂਦਾ ਵੱਧ ਤੋਂ ਵੱਧ ਸਮਰਥਿਤ 1×48 ਪੋਰਟ ਹੈ, ਜਿਵੇਂ ਕਿ ਫਿਨਿਸਰ ਦਾ ਫਲੈਕਸਗ੍ਰਿਡ ਟਵਿਨ 1×48) ਦਾ ਮਤਲਬ ਹੈ ਕਿ OXC ਮਾਪ ਨੂੰ ਵਧਾਉਣ ਲਈ ਸਾਰੇ ਹਾਰਡਵੇਅਰ ਨੂੰ ਬਦਲਣ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਜੋ ਕਿ ਮਹਿੰਗਾ ਹੈ ਅਤੇ ਮੌਜੂਦਾ ਉਪਕਰਣਾਂ ਦੀ ਮੁੜ ਵਰਤੋਂ ਨੂੰ ਰੋਕਦਾ ਹੈ।

Clos ਨੈੱਟਵਰਕਾਂ 'ਤੇ ਆਧਾਰਿਤ ਉੱਚ-ਆਯਾਮੀ OXC ਆਰਕੀਟੈਕਚਰ ਦੇ ਬਾਵਜੂਦ, ਇਹ ਅਜੇ ਵੀ ਮਹਿੰਗੇ M×N WSS 'ਤੇ ਨਿਰਭਰ ਕਰਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਵਾਧੇ ਵਾਲੇ ਅੱਪਗ੍ਰੇਡ ਲੋੜਾਂ ਨੂੰ ਪੂਰਾ ਕਰਨਾ ਮੁਸ਼ਕਲ ਹੋ ਜਾਂਦਾ ਹੈ।

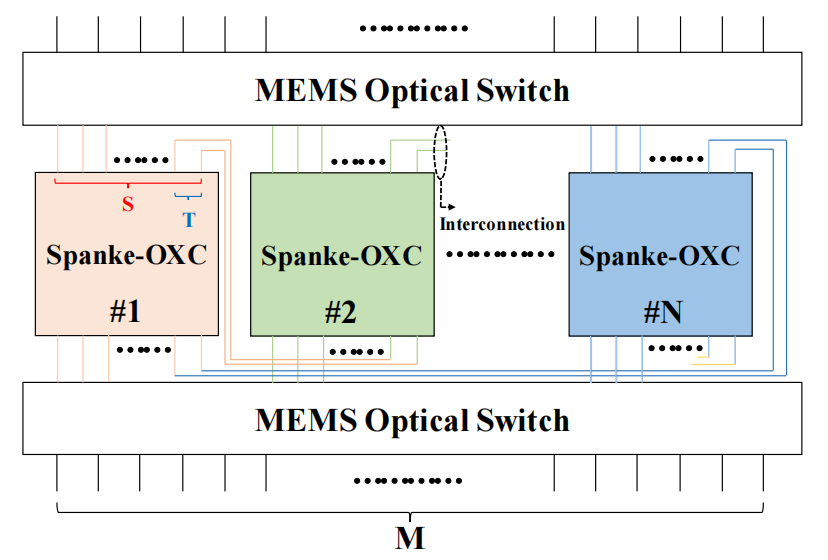

ਇਸ ਚੁਣੌਤੀ ਨੂੰ ਹੱਲ ਕਰਨ ਲਈ, ਖੋਜਕਰਤਾਵਾਂ ਨੇ ਇੱਕ ਨਵਾਂ ਹਾਈਬ੍ਰਿਡ ਆਰਕੀਟੈਕਚਰ ਪ੍ਰਸਤਾਵਿਤ ਕੀਤਾ ਹੈ: HMWC-OXC (ਹਾਈਬ੍ਰਿਡ MEMS ਅਤੇ WSS Clos Network)। ਮਾਈਕ੍ਰੋਇਲੈਕਟ੍ਰੋਮੈਕਨੀਕਲ ਸਿਸਟਮ (MEMS) ਅਤੇ WSS ਨੂੰ ਏਕੀਕ੍ਰਿਤ ਕਰਕੇ, ਇਹ ਆਰਕੀਟੈਕਚਰ "ਪੇ-ਐਜ਼-ਯੂ-ਗ੍ਰੋ" ਸਮਰੱਥਾਵਾਂ ਦਾ ਸਮਰਥਨ ਕਰਦੇ ਹੋਏ, ਲਗਭਗ-ਗੈਰ-ਬਲਾਕਿੰਗ ਪ੍ਰਦਰਸ਼ਨ ਨੂੰ ਬਣਾਈ ਰੱਖਦਾ ਹੈ, ਆਪਟੀਕਲ ਨੈੱਟਵਰਕ ਆਪਰੇਟਰਾਂ ਲਈ ਇੱਕ ਲਾਗਤ-ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਅੱਪਗ੍ਰੇਡ ਮਾਰਗ ਪ੍ਰਦਾਨ ਕਰਦਾ ਹੈ।

HMWC-OXC ਦਾ ਮੁੱਖ ਡਿਜ਼ਾਈਨ ਇਸਦੇ ਤਿੰਨ-ਲੇਅਰ ਕਲੋਸ ਨੈੱਟਵਰਕ ਢਾਂਚੇ ਵਿੱਚ ਹੈ।

ਚਿੱਤਰ: HMWC ਨੈੱਟਵਰਕਾਂ 'ਤੇ ਆਧਾਰਿਤ ਸਪੈਂਕ-OXC ਆਰਕੀਟੈਕਚਰ

ਉੱਚ-ਆਯਾਮੀ MEMS ਆਪਟੀਕਲ ਸਵਿੱਚ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਲੇਅਰਾਂ 'ਤੇ ਤੈਨਾਤ ਕੀਤੇ ਜਾਂਦੇ ਹਨ, ਜਿਵੇਂ ਕਿ 512×512 ਸਕੇਲ ਜੋ ਵਰਤਮਾਨ ਵਿੱਚ ਮੌਜੂਦਾ ਤਕਨਾਲੋਜੀ ਦੁਆਰਾ ਸਮਰਥਤ ਹੈ, ਇੱਕ ਵੱਡੀ-ਸਮਰੱਥਾ ਵਾਲਾ ਪੋਰਟ ਪੂਲ ਬਣਾਉਣ ਲਈ। ਵਿਚਕਾਰਲੀ ਪਰਤ ਵਿੱਚ ਕਈ ਛੋਟੇ ਸਪੈਂਕ-OXC ਮੋਡੀਊਲ ਹੁੰਦੇ ਹਨ, ਜੋ ਅੰਦਰੂਨੀ ਭੀੜ ਨੂੰ ਘਟਾਉਣ ਲਈ "ਟੀ-ਪੋਰਟ" ਰਾਹੀਂ ਆਪਸ ਵਿੱਚ ਜੁੜੇ ਹੁੰਦੇ ਹਨ।

ਸ਼ੁਰੂਆਤੀ ਪੜਾਅ ਵਿੱਚ, ਓਪਰੇਟਰ ਮੌਜੂਦਾ ਸਪੈਂਕ-ਓਐਕਸਸੀ (ਜਿਵੇਂ ਕਿ, 4×4 ਸਕੇਲ) ਦੇ ਆਧਾਰ 'ਤੇ ਬੁਨਿਆਦੀ ਢਾਂਚਾ ਬਣਾ ਸਕਦੇ ਹਨ, ਸਿਰਫ਼ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਲੇਅਰਾਂ 'ਤੇ MEMS ਸਵਿੱਚਾਂ (ਜਿਵੇਂ ਕਿ, 32×32) ਨੂੰ ਤੈਨਾਤ ਕਰ ਸਕਦੇ ਹਨ, ਜਦੋਂ ਕਿ ਵਿਚਕਾਰਲੀ ਪਰਤ ਵਿੱਚ ਇੱਕ ਸਿੰਗਲ ਸਪੈਂਕ-ਓਐਕਸਸੀ ਮੋਡੀਊਲ ਨੂੰ ਬਰਕਰਾਰ ਰੱਖਿਆ ਜਾ ਸਕਦਾ ਹੈ (ਇਸ ਸਥਿਤੀ ਵਿੱਚ, ਟੀ-ਪੋਰਟਾਂ ਦੀ ਗਿਣਤੀ ਜ਼ੀਰੋ ਹੈ)। ਜਿਵੇਂ-ਜਿਵੇਂ ਨੈੱਟਵਰਕ ਸਮਰੱਥਾ ਦੀਆਂ ਜ਼ਰੂਰਤਾਂ ਵਧਦੀਆਂ ਹਨ, ਨਵੇਂ ਸਪੈਂਕ-ਓਐਕਸਸੀ ਮੋਡੀਊਲ ਹੌਲੀ-ਹੌਲੀ ਵਿਚਕਾਰਲੀ ਪਰਤ ਵਿੱਚ ਸ਼ਾਮਲ ਕੀਤੇ ਜਾਂਦੇ ਹਨ, ਅਤੇ ਟੀ-ਪੋਰਟਾਂ ਨੂੰ ਮੋਡੀਊਲਾਂ ਨੂੰ ਜੋੜਨ ਲਈ ਕੌਂਫਿਗਰ ਕੀਤਾ ਜਾਂਦਾ ਹੈ।

ਉਦਾਹਰਨ ਲਈ, ਜਦੋਂ ਵਿਚਕਾਰਲੇ ਪਰਤ ਦੇ ਮਾਡਿਊਲਾਂ ਦੀ ਗਿਣਤੀ ਨੂੰ ਇੱਕ ਤੋਂ ਦੋ ਤੱਕ ਵਧਾਇਆ ਜਾਂਦਾ ਹੈ, ਤਾਂ ਟੀ-ਪੋਰਟਾਂ ਦੀ ਗਿਣਤੀ ਇੱਕ 'ਤੇ ਸੈੱਟ ਕੀਤੀ ਜਾਂਦੀ ਹੈ, ਜਿਸ ਨਾਲ ਕੁੱਲ ਮਾਪ ਚਾਰ ਤੋਂ ਛੇ ਹੋ ਜਾਂਦਾ ਹੈ।

ਚਿੱਤਰ: HMWC-OXC ਉਦਾਹਰਨ

ਇਹ ਪ੍ਰਕਿਰਿਆ ਪੈਰਾਮੀਟਰ ਸੀਮਾ M > N × (S − T) ਦੀ ਪਾਲਣਾ ਕਰਦੀ ਹੈ, ਜਿੱਥੇ:

M MEMS ਪੋਰਟਾਂ ਦੀ ਸੰਖਿਆ ਹੈ,

N ਵਿਚਕਾਰਲੇ ਪਰਤ ਮਾਡਿਊਲਾਂ ਦੀ ਸੰਖਿਆ ਹੈ,

S ਇੱਕ ਸਿੰਗਲ ਸਪੈਂਕ-OXC ਵਿੱਚ ਪੋਰਟਾਂ ਦੀ ਸੰਖਿਆ ਹੈ, ਅਤੇ

T ਆਪਸ ਵਿੱਚ ਜੁੜੇ ਪੋਰਟਾਂ ਦੀ ਸੰਖਿਆ ਹੈ।

ਇਹਨਾਂ ਪੈਰਾਮੀਟਰਾਂ ਨੂੰ ਗਤੀਸ਼ੀਲ ਤੌਰ 'ਤੇ ਐਡਜਸਟ ਕਰਕੇ, HMWC-OXC ਇੱਕ ਸ਼ੁਰੂਆਤੀ ਸਕੇਲ ਤੋਂ ਇੱਕ ਨਿਸ਼ਾਨਾ ਮਾਪ (ਜਿਵੇਂ ਕਿ, 64×64) ਤੱਕ ਹੌਲੀ-ਹੌਲੀ ਵਿਸਥਾਰ ਦਾ ਸਮਰਥਨ ਕਰ ਸਕਦਾ ਹੈ ਬਿਨਾਂ ਸਾਰੇ ਹਾਰਡਵੇਅਰ ਸਰੋਤਾਂ ਨੂੰ ਇੱਕੋ ਵਾਰ ਬਦਲੇ।

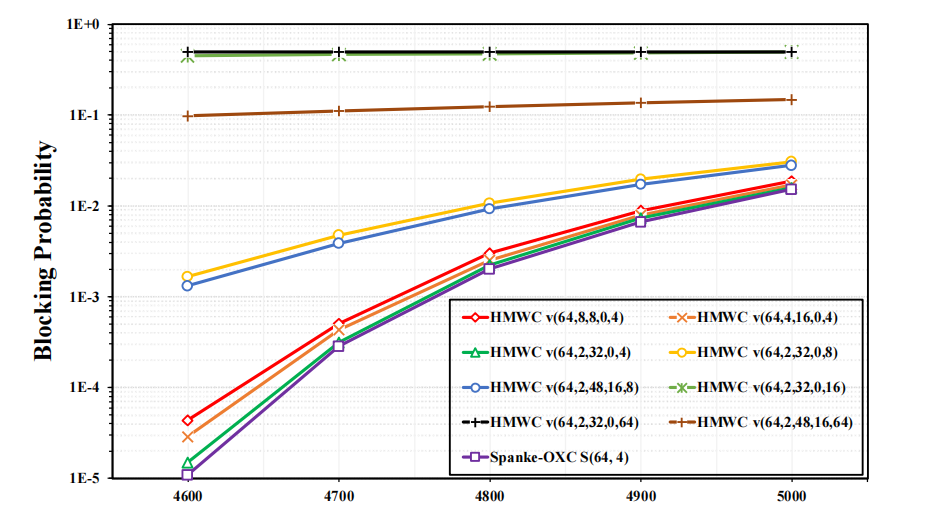

ਇਸ ਆਰਕੀਟੈਕਚਰ ਦੇ ਅਸਲ ਪ੍ਰਦਰਸ਼ਨ ਦੀ ਪੁਸ਼ਟੀ ਕਰਨ ਲਈ, ਖੋਜ ਟੀਮ ਨੇ ਗਤੀਸ਼ੀਲ ਆਪਟੀਕਲ ਮਾਰਗ ਬੇਨਤੀਆਂ ਦੇ ਅਧਾਰ ਤੇ ਸਿਮੂਲੇਸ਼ਨ ਪ੍ਰਯੋਗ ਕੀਤੇ।

ਚਿੱਤਰ: HMWC ਨੈੱਟਵਰਕ ਦੀ ਬਲਾਕਿੰਗ ਕਾਰਗੁਜ਼ਾਰੀ

ਸਿਮੂਲੇਸ਼ਨ ਇੱਕ ਏਰਲੈਂਗ ਟ੍ਰੈਫਿਕ ਮਾਡਲ ਦੀ ਵਰਤੋਂ ਕਰਦਾ ਹੈ, ਇਹ ਮੰਨ ਕੇ ਕਿ ਸੇਵਾ ਬੇਨਤੀਆਂ ਇੱਕ ਪੋਇਸਨ ਵੰਡ ਦੀ ਪਾਲਣਾ ਕਰਦੀਆਂ ਹਨ ਅਤੇ ਸੇਵਾ ਹੋਲਡ ਸਮਾਂ ਇੱਕ ਨਕਾਰਾਤਮਕ ਘਾਤ ਅੰਕੀ ਵੰਡ ਦੀ ਪਾਲਣਾ ਕਰਦਾ ਹੈ। ਕੁੱਲ ਟ੍ਰੈਫਿਕ ਲੋਡ 3100 ਏਰਲੈਂਗ 'ਤੇ ਸੈੱਟ ਕੀਤਾ ਗਿਆ ਹੈ। ਟੀਚਾ OXC ਮਾਪ 64×64 ਹੈ, ਅਤੇ ਇਨਪੁਟ ਅਤੇ ਆਉਟਪੁੱਟ ਲੇਅਰ MEMS ਸਕੇਲ ਵੀ 64×64 ਹੈ। ਵਿਚਕਾਰਲੀ ਪਰਤ ਸਪੈਂਕ-OXC ਮੋਡੀਊਲ ਸੰਰਚਨਾਵਾਂ ਵਿੱਚ 32×32 ਜਾਂ 48×48 ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਸ਼ਾਮਲ ਹਨ। ਦ੍ਰਿਸ਼ ਲੋੜਾਂ ਦੇ ਆਧਾਰ 'ਤੇ ਟੀ-ਪੋਰਟਾਂ ਦੀ ਗਿਣਤੀ 0 ਤੋਂ 16 ਤੱਕ ਹੁੰਦੀ ਹੈ।

ਨਤੀਜੇ ਦਰਸਾਉਂਦੇ ਹਨ ਕਿ, D = 4 ਦੇ ਦਿਸ਼ਾਤਮਕ ਆਯਾਮ ਵਾਲੇ ਦ੍ਰਿਸ਼ ਵਿੱਚ, HMWC-OXC ਦੀ ਬਲਾਕਿੰਗ ਸੰਭਾਵਨਾ ਰਵਾਇਤੀ ਸਪੈਂਕ-OXC ਬੇਸਲਾਈਨ (S(64,4)) ਦੇ ਨੇੜੇ ਹੈ। ਉਦਾਹਰਨ ਲਈ, v(64,2,32,0,4) ਸੰਰਚਨਾ ਦੀ ਵਰਤੋਂ ਕਰਦੇ ਹੋਏ, ਬਲਾਕਿੰਗ ਸੰਭਾਵਨਾ ਮੱਧਮ ਲੋਡ ਦੇ ਅਧੀਨ ਸਿਰਫ ਲਗਭਗ 5% ਵਧਦੀ ਹੈ। ਜਦੋਂ ਦਿਸ਼ਾਤਮਕ ਆਯਾਮ D = 8 ਤੱਕ ਵਧਦਾ ਹੈ, ਤਾਂ "ਟਰੰਕ ਪ੍ਰਭਾਵ" ਅਤੇ ਹਰੇਕ ਦਿਸ਼ਾ ਵਿੱਚ ਫਾਈਬਰ ਲੰਬਾਈ ਵਿੱਚ ਕਮੀ ਦੇ ਕਾਰਨ ਬਲਾਕਿੰਗ ਸੰਭਾਵਨਾ ਵਧ ਜਾਂਦੀ ਹੈ। ਹਾਲਾਂਕਿ, ਇਸ ਮੁੱਦੇ ਨੂੰ ਟੀ-ਪੋਰਟਾਂ ਦੀ ਗਿਣਤੀ ਵਧਾ ਕੇ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਢੰਗ ਨਾਲ ਘੱਟ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ (ਉਦਾਹਰਣ ਵਜੋਂ, v(64,2,48,16,8) ਸੰਰਚਨਾ)।

ਖਾਸ ਤੌਰ 'ਤੇ, ਹਾਲਾਂਕਿ ਮਿਡ-ਲੇਅਰ ਮੋਡੀਊਲ ਦੇ ਜੋੜ ਨਾਲ ਟੀ-ਪੋਰਟ ਵਿਵਾਦ ਦੇ ਕਾਰਨ ਅੰਦਰੂਨੀ ਬਲਾਕਿੰਗ ਹੋ ਸਕਦੀ ਹੈ, ਫਿਰ ਵੀ ਸਮੁੱਚਾ ਆਰਕੀਟੈਕਚਰ ਢੁਕਵੀਂ ਸੰਰਚਨਾ ਦੁਆਰਾ ਅਨੁਕੂਲਿਤ ਪ੍ਰਦਰਸ਼ਨ ਪ੍ਰਾਪਤ ਕਰ ਸਕਦਾ ਹੈ।

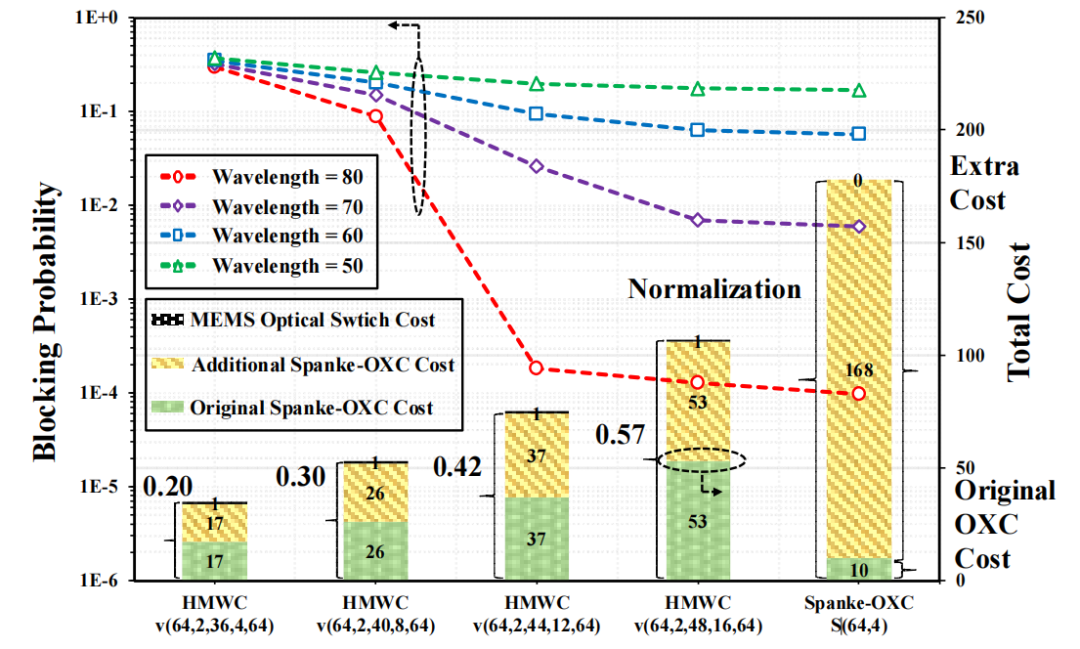

ਇੱਕ ਲਾਗਤ ਵਿਸ਼ਲੇਸ਼ਣ HMWC-OXC ਦੇ ਫਾਇਦਿਆਂ ਨੂੰ ਹੋਰ ਉਜਾਗਰ ਕਰਦਾ ਹੈ, ਜਿਵੇਂ ਕਿ ਹੇਠਾਂ ਦਿੱਤੀ ਤਸਵੀਰ ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ।

ਚਿੱਤਰ: ਵੱਖ-ਵੱਖ OXC ਆਰਕੀਟੈਕਚਰ ਦੀ ਬਲਾਕਿੰਗ ਸੰਭਾਵਨਾ ਅਤੇ ਲਾਗਤ

80 ਤਰੰਗ-ਲੰਬਾਈ/ਫਾਈਬਰ ਵਾਲੇ ਉੱਚ-ਘਣਤਾ ਵਾਲੇ ਦ੍ਰਿਸ਼ਾਂ ਵਿੱਚ, HMWC-OXC (v(64,2,44,12,64)) ਰਵਾਇਤੀ ਸਪੈਂਕ-OXC ਦੇ ਮੁਕਾਬਲੇ ਲਾਗਤਾਂ ਨੂੰ 40% ਘਟਾ ਸਕਦਾ ਹੈ। ਘੱਟ-ਤਰੰਗ-ਲੰਬਾਈ ਵਾਲੇ ਦ੍ਰਿਸ਼ਾਂ (ਜਿਵੇਂ ਕਿ, 50 ਤਰੰਗ-ਲੰਬਾਈ/ਫਾਈਬਰ) ਵਿੱਚ, ਲੋੜੀਂਦੇ ਟੀ-ਪੋਰਟਾਂ ਦੀ ਘਟੀ ਹੋਈ ਗਿਣਤੀ (ਜਿਵੇਂ ਕਿ, v(64,2,36,4,64)) ਦੇ ਕਾਰਨ ਲਾਗਤ ਫਾਇਦਾ ਹੋਰ ਵੀ ਮਹੱਤਵਪੂਰਨ ਹੈ।

ਇਹ ਆਰਥਿਕ ਲਾਭ MEMS ਸਵਿੱਚਾਂ ਦੀ ਉੱਚ ਪੋਰਟ ਘਣਤਾ ਅਤੇ ਇੱਕ ਮਾਡਿਊਲਰ ਵਿਸਥਾਰ ਰਣਨੀਤੀ ਦੇ ਸੁਮੇਲ ਤੋਂ ਪੈਦਾ ਹੁੰਦਾ ਹੈ, ਜੋ ਨਾ ਸਿਰਫ਼ ਵੱਡੇ ਪੱਧਰ 'ਤੇ WSS ਬਦਲਣ ਦੇ ਖਰਚੇ ਤੋਂ ਬਚਦਾ ਹੈ ਬਲਕਿ ਮੌਜੂਦਾ ਸਪੈਂਕ-OXC ਮੋਡੀਊਲਾਂ ਦੀ ਮੁੜ ਵਰਤੋਂ ਕਰਕੇ ਵਾਧੇ ਵਾਲੀਆਂ ਲਾਗਤਾਂ ਨੂੰ ਵੀ ਘਟਾਉਂਦਾ ਹੈ। ਸਿਮੂਲੇਸ਼ਨ ਨਤੀਜੇ ਇਹ ਵੀ ਦਰਸਾਉਂਦੇ ਹਨ ਕਿ ਮੱਧ-ਪਰਤ ਮੋਡੀਊਲਾਂ ਦੀ ਗਿਣਤੀ ਅਤੇ ਟੀ-ਪੋਰਟਾਂ ਦੇ ਅਨੁਪਾਤ ਨੂੰ ਵਿਵਸਥਿਤ ਕਰਕੇ, HMWC-OXC ਵੱਖ-ਵੱਖ ਤਰੰਗ-ਲੰਬਾਈ ਸਮਰੱਥਾ ਅਤੇ ਦਿਸ਼ਾ ਸੰਰਚਨਾਵਾਂ ਦੇ ਅਧੀਨ ਪ੍ਰਦਰਸ਼ਨ ਅਤੇ ਲਾਗਤ ਨੂੰ ਲਚਕਦਾਰ ਢੰਗ ਨਾਲ ਸੰਤੁਲਿਤ ਕਰ ਸਕਦਾ ਹੈ, ਜਿਸ ਨਾਲ ਓਪਰੇਟਰਾਂ ਨੂੰ ਬਹੁ-ਆਯਾਮੀ ਅਨੁਕੂਲਤਾ ਦੇ ਮੌਕੇ ਪ੍ਰਦਾਨ ਹੁੰਦੇ ਹਨ।

ਭਵਿੱਖ ਦੀ ਖੋਜ ਅੰਦਰੂਨੀ ਸਰੋਤ ਉਪਯੋਗਤਾ ਨੂੰ ਅਨੁਕੂਲ ਬਣਾਉਣ ਲਈ ਗਤੀਸ਼ੀਲ ਟੀ-ਪੋਰਟ ਵੰਡ ਐਲਗੋਰਿਦਮ ਦੀ ਹੋਰ ਪੜਚੋਲ ਕਰ ਸਕਦੀ ਹੈ। ਇਸ ਤੋਂ ਇਲਾਵਾ, MEMS ਨਿਰਮਾਣ ਪ੍ਰਕਿਰਿਆਵਾਂ ਵਿੱਚ ਤਰੱਕੀ ਦੇ ਨਾਲ, ਉੱਚ-ਅਯਾਮੀ ਸਵਿੱਚਾਂ ਦਾ ਏਕੀਕਰਨ ਇਸ ਆਰਕੀਟੈਕਚਰ ਦੀ ਸਕੇਲੇਬਿਲਟੀ ਨੂੰ ਹੋਰ ਵਧਾਏਗਾ। ਆਪਟੀਕਲ ਨੈੱਟਵਰਕ ਆਪਰੇਟਰਾਂ ਲਈ, ਇਹ ਆਰਕੀਟੈਕਚਰ ਖਾਸ ਤੌਰ 'ਤੇ ਅਨਿਸ਼ਚਿਤ ਟ੍ਰੈਫਿਕ ਵਾਧੇ ਵਾਲੇ ਦ੍ਰਿਸ਼ਾਂ ਲਈ ਢੁਕਵਾਂ ਹੈ, ਇੱਕ ਲਚਕੀਲਾ ਅਤੇ ਸਕੇਲੇਬਲ ਆਲ-ਆਪਟੀਕਲ ਬੈਕਬੋਨ ਨੈੱਟਵਰਕ ਬਣਾਉਣ ਲਈ ਇੱਕ ਵਿਹਾਰਕ ਤਕਨੀਕੀ ਹੱਲ ਪ੍ਰਦਾਨ ਕਰਦਾ ਹੈ।

ਪੋਸਟ ਸਮਾਂ: ਅਗਸਤ-21-2025